Protocole de cohérence de cache

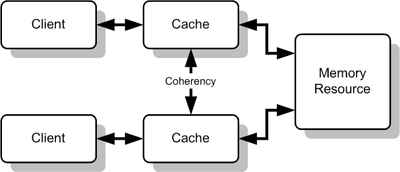

Un cache peut être utilisé pour améliorer les performances d'accès à une ressource donnée. Lorsqu'il existe plusieurs caches de ce type pour une même ressource, comme le montre l'image, cela peut entraîner des problèmes. La cohérence des caches ou Cache coherency fait référence à un certain nombre de façons de s'assurer que toutes les caches de la ressource ont les mêmes données, et que les données dans les caches ont un sens (appelé intégrité des données). La cohérence du cache est un cas particulier de cohérence de la mémoire.

Il peut y avoir des problèmes s'il y a plusieurs caches d'une ressource mémoire commune, car les données dans le cache peuvent ne plus avoir de sens, ou un cache peut ne plus avoir les mêmes données que les autres. Un cas fréquent où le problème se pose est celui du cache des unités centrales de traitement dans un système multiprocesseur. Comme le montre la figure, si le client supérieur possède une copie d'un bloc de mémoire d'une lecture précédente et que le client inférieur modifie ce bloc de mémoire, le client supérieur pourrait se retrouver avec un cache de mémoire non valide, sans le savoir. La cohérence du cache est là pour gérer de tels conflits et maintenir la cohérence entre le cache et la mémoire.

Plusieurs caches de ressources partagées

Définition

La cohérence définit le comportement des lectures et des écritures dans le même emplacement mémoire. Les caches sont cohérentes, si toutes les conditions suivantes sont remplies :

- Lorsqu'un processeur P lit un emplacement X, après avoir écrit à cet emplacement, P doit obtenir la valeur qu'il a écrite, si aucun autre processeur n'a écrit une autre valeur à cet emplacement. Cela est également vrai pour les systèmes à monoprocesseur, cela signifie que la mémoire est capable de conserver une valeur écrite.

- Supposons qu'il y ait deux processeurs, P1 et P2, et que P1 écrive une valeur X1, et qu'ensuite, P2 écrive une valeur X2, si P1 lit la valeur, il doit obtenir la valeur écrite par P2, X2, et non la valeur qu'il a écrite, X1, s'il n'y a pas d'autres écritures entre les deux. Cela signifie que la vision de la mémoire est cohérente. Si les processeurs peuvent lire la même ancienne valeur après l'écriture effectuée par P2, la mémoire ne serait pas cohérente.

- Il ne peut y avoir qu'une seule écriture à la fois à un certain endroit de la mémoire. S'il y a plusieurs écritures, elles doivent se produire l'une après l'autre. En d'autres termes, si l'emplacement X a reçu deux valeurs différentes A et B, dans cet ordre, par deux processeurs quelconques, les processeurs ne peuvent jamais lire l'emplacement X comme B et ensuite le lire comme A. L'emplacement X doit être vu avec les valeurs A et B dans cet ordre.

Ces conditions sont définies en supposant que les opérations de lecture et d'écriture sont effectuées instantanément. Cependant, cela ne se produit pas dans le matériel informatique en raison de la latence de la mémoire et d'autres aspects de l'architecture. Une écriture par le processeur X peut ne pas être vue par une lecture du processeur Y si la lecture est effectuée dans un délai très court après l'écriture. Le modèle de cohérence de la mémoire définit quand une valeur écrite doit être vue par une instruction de lecture suivante faite par les autres processeurs.

Mécanismes de cohérence du cache

- Les mécanismes de cohérence basés sur des répertoires maintiennent un répertoire central des blocs mis en cache.

- L'espionnage est le processus par lequel chaque cache surveille les lignes d'adresse pour les accès aux emplacements de mémoire qui se trouvent dans son cache. Lorsqu'une opération d'écriture est observée dans un emplacement dont la mémoire cache possède une copie, le contrôleur de la mémoire cache invalide sa propre copie de l'emplacement de mémoire fouiné.

- Le snarfing est un système dans lequel un contrôleur de cache surveille à la fois l'adresse et les données pour tenter de mettre à jour sa propre copie d'un emplacement mémoire lorsqu'un deuxième maître modifie un emplacement de la mémoire principale.

Les systèmes de mémoire partagée distribuée imitent ces mécanismes afin de maintenir la cohérence entre les blocs de mémoire dans les systèmes faiblement couplés.

Les deux types de cohérence les plus couramment étudiés sont l'espionnage et l'annuaire. Chacune a ses propres avantages et inconvénients. Les protocoles d'espionnage ont tendance à être plus rapides, si une bande passante suffisante est disponible, puisque toutes les transactions sont une demande/réponse vue par tous les processeurs. L'inconvénient est que l'espionnage n'est pas évolutif. Chaque requête doit être diffusée à tous les nœuds d'un système. À mesure que le système s'agrandit, la taille du bus (logique ou physique) et la largeur de bande qu'il fournit doivent augmenter. Les annuaires, d'autre part, ont tendance à avoir des latences plus longues (avec une demande/transfert de réponse de 3 sauts) mais utilisent beaucoup moins de bande passante puisque les messages sont point à point et non diffusés. Pour cette raison, beaucoup de grands systèmes (>64 processeurs) utilisent ce type de cohérence de cache.

Questions et réponses

Q : Qu'est-ce que la cohérence de la mémoire cache ?

R : La cohérence du cache consiste à s'assurer que tous les caches d'une ressource contiennent les mêmes données et que les données contenues dans les caches sont cohérentes (intégrité des données).

Q : Quel est l'objectif de la cohérence de la mémoire cache ?

R : La cohérence de la mémoire cache a pour but de gérer les conflits entre plusieurs caches d'une ressource mémoire commune et de maintenir la cohérence entre la mémoire cache et la mémoire.

Q : Quelles peuvent être les conséquences de l'absence de cohérence de la mémoire cache ?

R : Sans cohérence de la mémoire cache, les données de la mémoire cache peuvent ne plus avoir de sens, ou une mémoire cache peut ne plus avoir les mêmes données que les autres, ce qui peut entraîner des incohérences et des erreurs.

Q : Quel est le cas le plus fréquent où des problèmes de cohérence de la mémoire cache se produisent ?

R : La mémoire cache des unités centrales dans un système multiprocessus est un cas courant où des problèmes de cohérence de la mémoire cache se produisent.

Q : Comment fonctionne la cohérence de la mémoire cache ?

R : La cohérence de la mémoire cache permet de s'assurer que tous les caches d'une ressource contiennent les mêmes données et que les données contenues dans les caches sont cohérentes grâce à diverses méthodes.

Q : Qu'entend-on par cohérence de la mémoire ?

R : La cohérence de la mémoire fait référence à la cohérence des données dans une ressource de mémoire partagée.

Q : Comment la cohérence de la mémoire cache peut-elle améliorer les performances ?

R : La cohérence de la mémoire cache peut améliorer les performances en permettant un accès plus rapide et plus efficace à une ressource donnée.

Rechercher dans l'encyclopédie